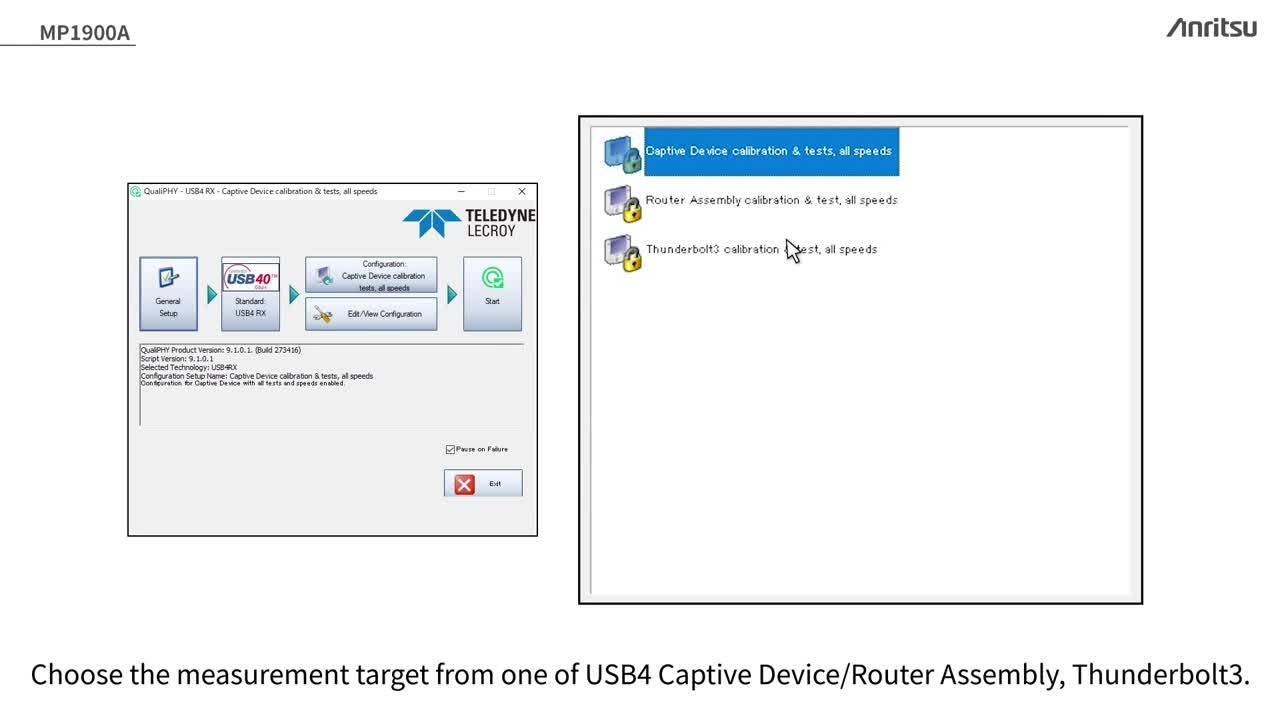

This video explains the receiver test calibration and procedure required by Type-C integration USB4 compliance test.

Want a head start on tomorrow's technologies? Sign up for monthly insights

Other content in this Stream

This paper examines the crucial PCIe 5.0 serializer/deserializer (SerDes) tests.

52:17

52:17This webinar will provide an overview of the methods for solving some of the new test and measurement receiver challenges for PCIE® 5.0 at 32.0 GT/s.

This eBook provides guidance on what to consider when developing a high-speed data transmission product or system and the associated test concerns.

1:02:57

1:02:57This webinar will provide an overview of the methods for solving some of the new test and measurement receiver challenges for PCIE® 5.0 at 32.0 GT/s.

45:20

45:20PCI Express® (PCIe®) technology has long met the bandwidth and reliability demands of traditional high-performance data center computing, which is why it is being leveraged by the automobile industry

1:15

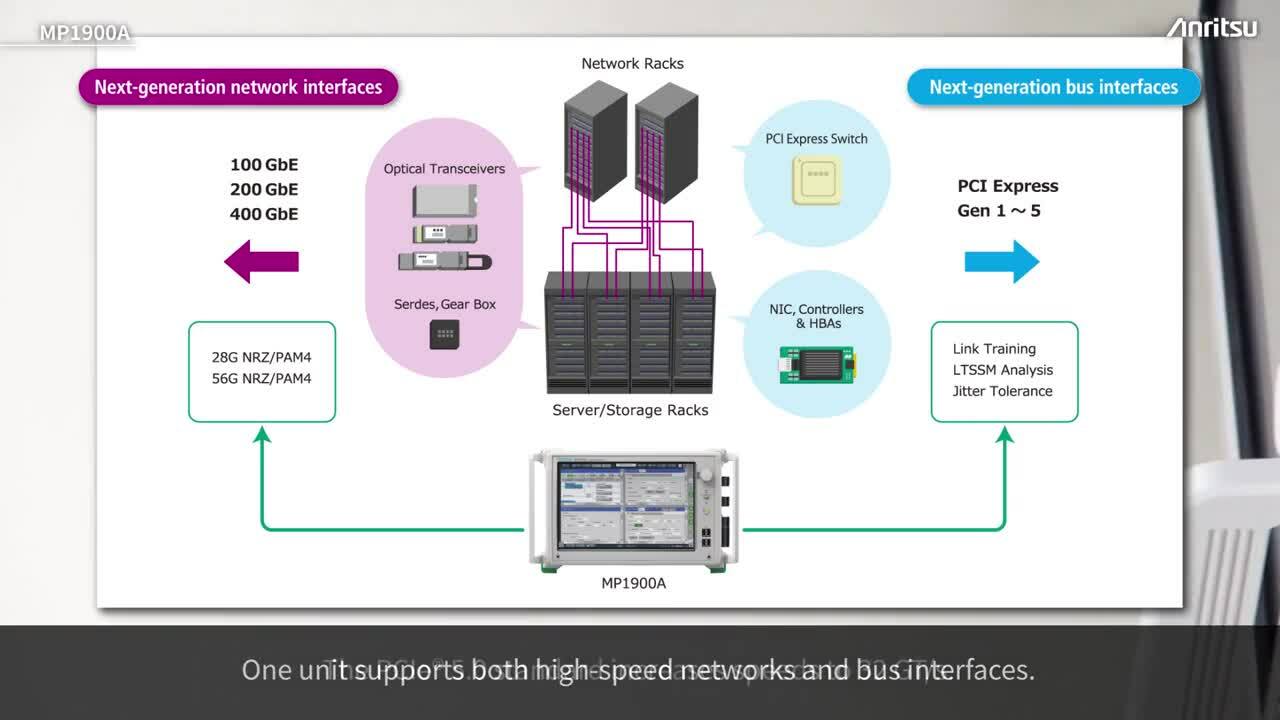

1:15The Anritsu MP1900A SQA-R is a high-performance BERT for measuring the PHY layer of high-speed interfaces. One unit supports both high-speed networks and bus interfaces. The PCIe® 5.0 standard increas

PCIe 5.0 works at 32 GT/s data rate per lane, double its predecessor

2:58

2:58The Signal Quality Analyzer-R MP1900A series of high-performance BER testers (BERT) is designed to measure 400GbE and future 800GbE interfaces and supports more accurate BER evaluation of PAM4 interfa

As a developer of automotive solutions leveraging PCIe technology, it is critical that you have the right technology to ensure your solutions are compliant.

36:20

36:20PCIe 6.0 introduces Flow Control Unit (FLIT) encoding to allow forward error correction (FEC) on fixed-size packets. Stress testing PCIe hardware includes addressing this new protocol approach.

Read this Design World article to learn about the evolution of PCIe and the specifics of PCIe 6.0 as compared to previous specifications including the integration of PAM4 technology and FLIT encoding

33:21

33:21PAM4 BER & JTOL Test Solutions for PCIe 6 & Beyond with Anritsu

44:41

44:41Watch this webinar to learn about Automotive technology and testing in Telematics, Infotainment and ADAS, including 5G/cellular, server applications, and more

This paper outlines the enhanced PCIe 6.0 technologies, such as PAM4, Forward Error Correction (FEC) and link equalization

28:09

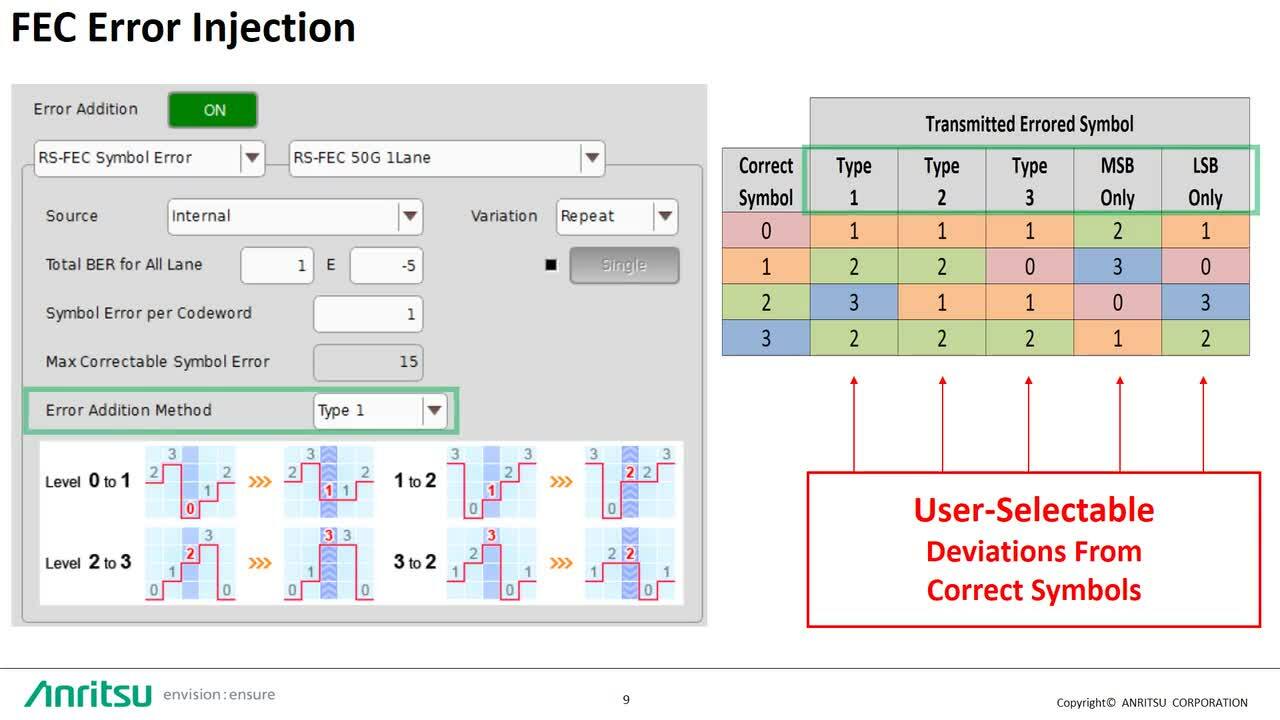

28:09High-speed and large-capacity transmission standards using PAM4 signaling, such as 400 GbE, stipulate the use of Forward Error Correction (FEC) to assure transmission quality

3:17

3:17The Signal Quality Analyzer-R MP1900A series is a high-performance BERT with excellent expandability for supporting Physical layer evaluations. One unit can be used to evaluate both next-generation ne

FEC is a key technology for assuring the quality of large-capacity transmissions, such as 100 and 400 GbE.

5:12

5:12FEC technology is key to ensure quality of high-speed transmissions. The Signal Quality Analyzer-R MP1900A supports NRZ & PAM4 signals for 25/50/100/200/400G multi-channel applications. Features incl