PCI Express® I/O bandwidth has doubled every 3 years on average thereby leading to an increased demand for this full-duplex high-speed bus architecture. As the industry begins deploying the 5.0 revision with a bit rate of 32 GT/s, new trends and guidelines emerge for receiver compliance and validation. This webinar will provide an overview of the methods for solving some of the new test and measurement receiver challenges for PCIE® 5.0 at 32.0 GT/s.

The key topics covered in this presentation are as follows:

• Status of 5.0 specifications including Base, CEM, and the test specifications

• PCI-SIG® 5.0 compliance program

• Challenges and latest guidelines on 32 GT/s receiver testing from industry experts

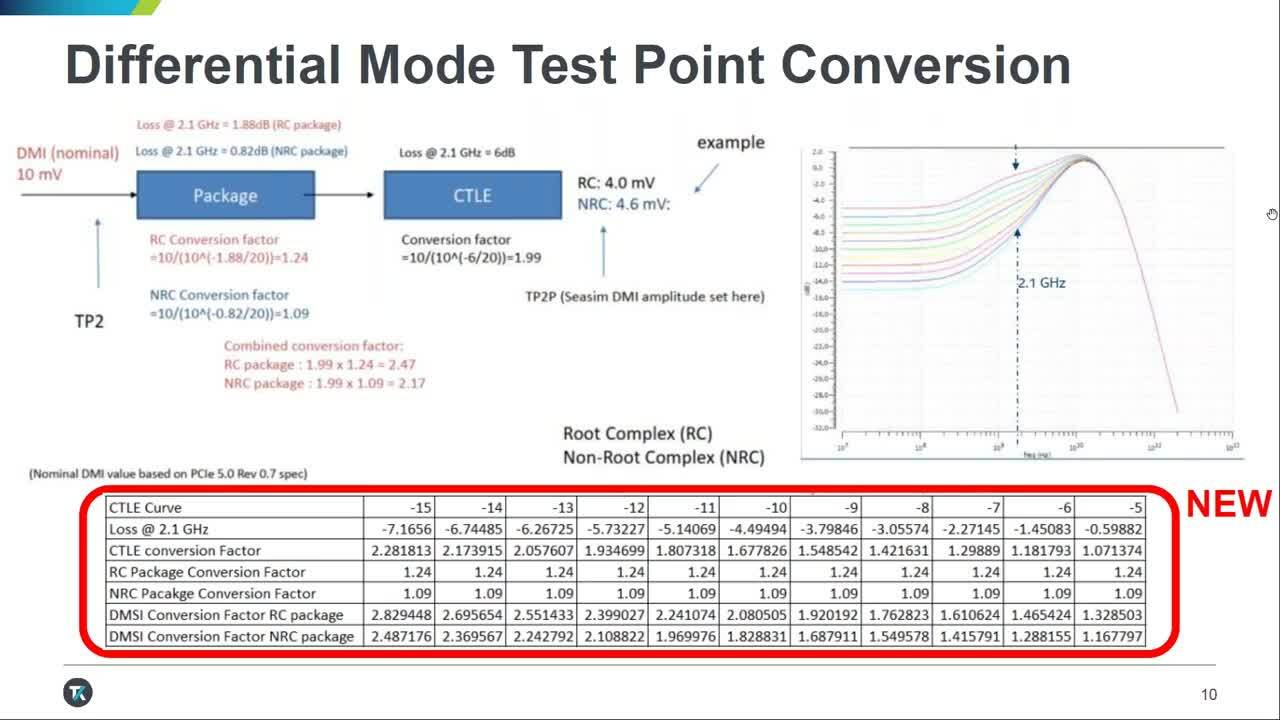

• Nuances of the 32 GT/s stressed eye calibration

• Handling high loss backchannels with equalization

• Thoughts on Rx testing with and without spread spectrum clocking (SSC)

• Solving validation challenges with a receiver solution from Anritsu & Tektronix